General-purpose MCU with EEPROM, 12bit-ADC, LIN Communication

# BS9000AM Series V1.0

General-purpose MCU With EEPROM, 12bit-ADC, LIN Communication

V1.0 2022-05-30

### BS9000AM Series V1.0

General-purpose MCU with EEPROM, 12bit-ADC, LIN Communication

### **Table of Contents**

| 1 | B   | BS9000AM SERIES MCU OVERVIEW                                        | 9  |

|---|-----|---------------------------------------------------------------------|----|

|   | 1.1 | Features                                                            | 9  |

|   | 1.2 | DESCRIPTION                                                         | 10 |

|   | 1.3 | System Block Diagram                                                | 10 |

|   | 1.4 | CLOCK DIAGRAM                                                       | 11 |

|   | 1.5 | SELECTION TABLE                                                     |    |

|   | 1.6 | PIN CONFIGURATION                                                   | 13 |

|   | 1.  | .6.1 QFN20                                                          |    |

|   | 1.  | .6.2 TSSOP28                                                        | 14 |

|   | 1.7 | PIN FUNCTIONS                                                       | 15 |

| 2 | E   | ELECTRICAL CHARACTERISTICS                                          | 20 |

|   | 2.1 | AC CHARACTERISTICS                                                  | 20 |

|   | 2.2 | DC CHARACTERISTICS                                                  | 21 |

|   | 2.3 | ADC CHARACTERISTICS                                                 | 25 |

|   | 2.4 | ABSOLUTE MAXIMUM RATINGS                                            | 26 |

| 3 | N   | MEMORIES                                                            | 27 |

|   | 3.1 | FLASH                                                               |    |

|   | 3.2 | FLASH READ AND WRITE PROTECTION                                     |    |

|   | 3.  | .2.1 FLASH Write Protection                                         |    |

|   | 3.  | .2.2 FLASH Read Protection                                          |    |

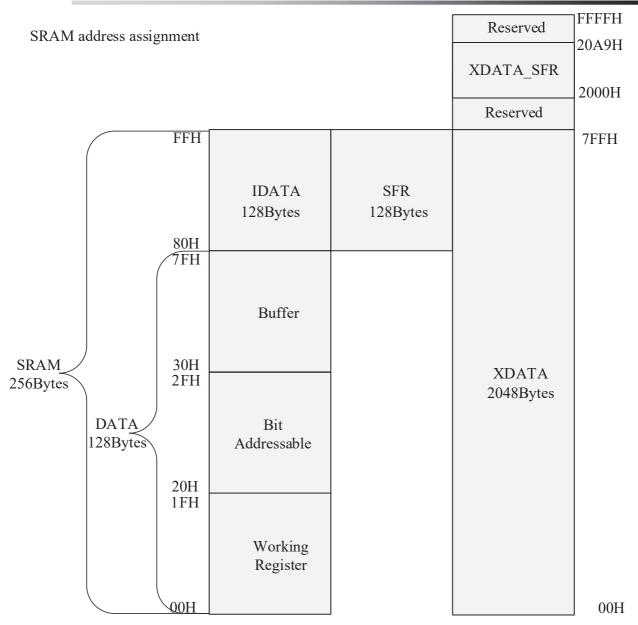

|   | 3.3 | SRAM                                                                |    |

|   | 3.4 | EEPROM                                                              |    |

|   | 3.4 | .4.1 Page Erase                                                     |    |

|   | 3.4 | .4.2 Byte Programming                                               |    |

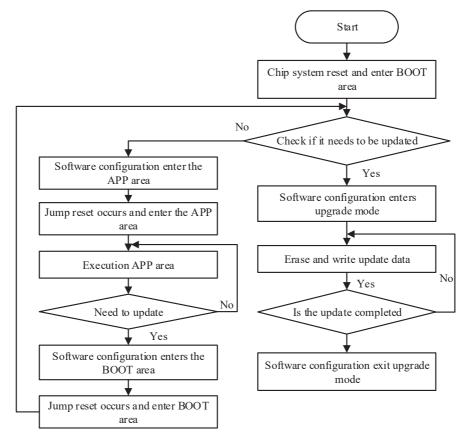

|   | 3.5 | IAP OPERATION                                                       |    |

|   | 3.  | .5.1 Program Upgrade                                                |    |

|   | 3.  | .5.2 FLASH IAP Erase Operation                                      |    |

|   | 3.  | .5.3 FLASH IAP bit Write                                            |    |

|   | 3.  | .5.4 FLASH IAP Operation                                            |    |

|   | 3.6 | REGISTERS FOR MEMORY                                                |    |

|   | 3.  | .6.1 Interrupt Vector Table Offset Register (OFFSET_ADDR_L)         |    |

|   | 3.  | .6.2 Vector Table Offset Interrupt Address Register (OFFSET_ADDR_H) |    |

|   | 3.  | .6.3 Address Control Register (SPROG_ADDR_H)                        |    |

|   | 3.  | .6.4 Address Control Register (SPROG_ADDR_L)                        |    |

|   | 3.  | .6.5 Data Register (SPROG_DATA)                                     | 40 |

|   | 3.  | .6.6 Command register (SPROG_CMD)                                   | 41 |

|   | 3.  | .6.7 Erase and Write Time Control Register (SPROG_TIM)              | 41 |

BYD)

### BS9000AM Series V1.0

|   | 3.6. | .8  | BOOT Status Register (FLASH_BOOT_EN)                                  | 41 |

|---|------|-----|-----------------------------------------------------------------------|----|

|   | 3.6. | .9  | Write Protect Range Configuration Register (FLASH_WPROTECT_PAGE)      | 42 |

| 4 | SY   | /ST | EM                                                                    | 43 |

|   | 4.1  |     | DCK                                                                   | 13 |

|   |      |     | SET SYSTEM                                                            |    |

|   |      |     | DT                                                                    |    |

|   |      |     | ERATING MODES                                                         |    |

|   |      |     | TCHDOG TIMER (WDT)                                                    |    |

|   |      |     | STEM REGISTERS                                                        |    |

|   | 4.6. |     | Software Reset Register (SOFT_RST)                                    |    |

|   | 4.6. |     | Reset Flag Register (RST_STAT)                                        |    |

|   | 4.6. |     | Module Switching Control Register (PD_ANA)                            |    |

|   | 4.6. |     | BOR Threshold Selection Register (BOR_SEL)                            |    |

|   | 4.6. | .5  | LVDT Control Register (LVDT_SEL)                                      | 53 |

|   | 4.6. | .6  | Test Clock Register (SFR_TEST_SEL1)                                   | 53 |

|   | 4.6. | .7  | Sleep Control Register (PCON)                                         | 54 |

|   | 4.6. | .8  | Clock control register (SYS_CLK_CFG)                                  | 55 |

|   | 4.6. | .9  | LVDT Rising/Falling Voltage Interrupt Status Register (INT_POBO_STAT) | 55 |

|   | 4.6. | .10 | WDT Test Mode Register (WDT_TEST_EN)                                  | 56 |

|   | 4.6. | .11 | WDT Clock Selection Register (WDT_CLK_SEL)                            |    |

|   | 4.6. | .12 | WDT Overflow Configuration Register (WDT_CTRL)                        |    |

|   | 4.6. | .13 | WDT Enable Configuration Register (WDT_EN)                            | 57 |

|   | 4.6. | .14 | WDT/Timer2 Interrupt Status Register (INT_PE_STAT)                    | 57 |

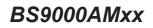

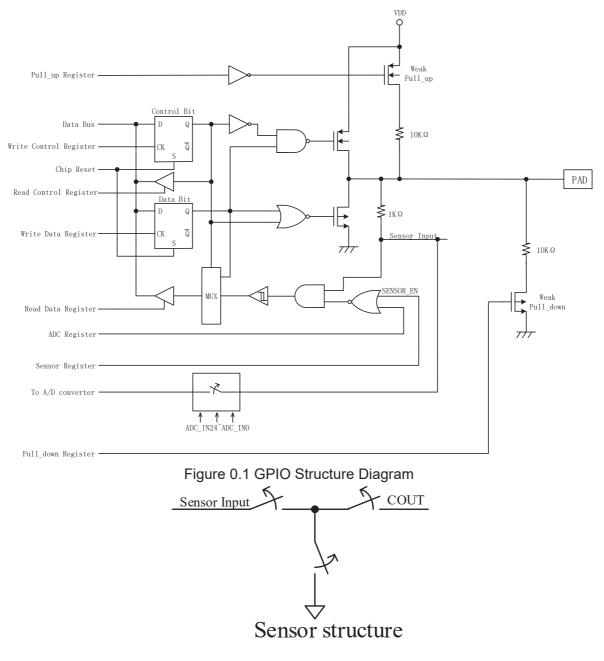

| 5 | GF   | PIO |                                                                       | 59 |

|   | 5.1  | Des | SCRIPTION                                                             | 59 |

|   | 5.2  | GP  | IO REGISTERS                                                          | 61 |

|   | 5.2. | .1  | Data Registers                                                        | 61 |

|   | 5.2. | .2  | Output Control Hold Register When Reset (PD_HOLD_EN)                  | 64 |

|   | 5.2. | .3  | Direction Registers                                                   |    |

|   | 5.2. | .4  | Pull-up Resistor Enable Registers                                     | 66 |

|   | 5.2. | .5  | Pull-down Resistor Enable Registers                                   | 68 |

|   | 5.2. | .6  | Open Drain Output Enable Register(ODRAIN_EN)                          |    |

|   | 5.3  | I/O | MULTIPLEXING TABLES                                                   | 70 |

|   | 5.3. | .1  | SPI I/O Multiplexing (SPI_IO_SEL)                                     | 70 |

|   | 5.3. | .2  | UART I/O Multiplexing (UART_IO_SEL)                                   | 70 |

|   | 5.3. | .3  | SCI I/O Multiplexing (SCI_IO_SEL)                                     | 71 |

|   | 5.3. | .4  | PWM I/O Multiplexing                                                  | 71 |

|   | 5.3. | .5  | IIC I/O Multiplexing (IIC_IO_SEL)                                     | 72 |

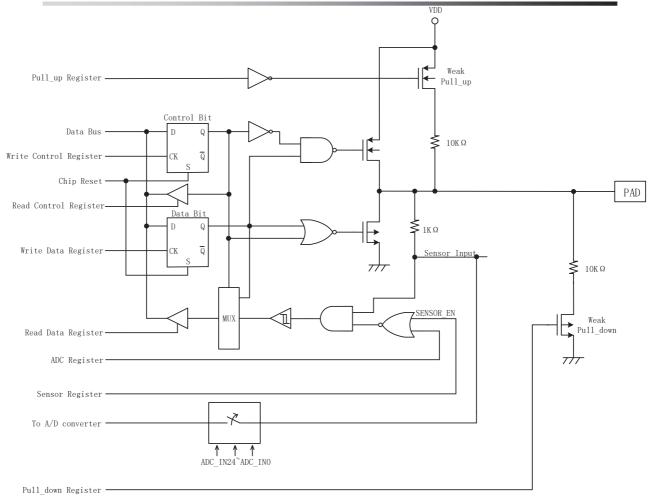

|   | 5.4  | GΡ  | IO CONFIGURATION FLOW DIAGRAM                                         | 73 |

| 6 | IN   | TEF | RRUPT                                                                 | 74 |

### BS9000AM Series V1.0

| 6.1                                                                                                | Int                                                                                                                                                   | ERRUPT SOURCES AND ENTRIES                                 | 75     |

|----------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------|--------|

| 6.2                                                                                                | INT                                                                                                                                                   | ERRUPT FUNCTIONS                                           | 77     |

| e                                                                                                  | 5.2.1                                                                                                                                                 | Interrupt Response                                         | 77     |

| e                                                                                                  | 5.2.2                                                                                                                                                 | Interrupt Handling                                         | 77     |

| 6                                                                                                  | 6.2.3                                                                                                                                                 | Interrupt Sampling                                         | 78     |

| 6.3                                                                                                | INT                                                                                                                                                   | ERRUPT WAKEUP                                              | 78     |

| 6.4                                                                                                | INT                                                                                                                                                   | ERRUPT REGISTERS                                           | 79     |

| 6                                                                                                  | 6.4.1                                                                                                                                                 | Interrupt Enable Register 0(IEN0)                          | 79     |

| 6                                                                                                  | 6.4.2                                                                                                                                                 | Interrupt Priority Register 0 (IPL0)                       | 80     |

| 6                                                                                                  | 6.4.3                                                                                                                                                 | Interrupt Flag Register (TCON)                             | 80     |

| 6                                                                                                  | 6.4.4                                                                                                                                                 | Interrupt Enable Register 1 (IEN1)                         | 81     |

| e                                                                                                  | 6.4.5                                                                                                                                                 | Interrupt Priority Register 1 (IPL1)                       | 82     |

| 6                                                                                                  | 6.4.6                                                                                                                                                 | Interrupt Flag Register 1(IRCON1)                          | 83     |

| 6                                                                                                  | 6.4.7                                                                                                                                                 | Interrupt Enable Register 2(IEN2)                          | 83     |

| 6                                                                                                  | 6.4.8                                                                                                                                                 | Interrupt Priority Register 2 (IPL2)                       | 84     |

| 6                                                                                                  | 5.4.9                                                                                                                                                 | Interrupt Flag Register 2 (IRCON2)                         |        |

| 6                                                                                                  | 5.4.10                                                                                                                                                | <b>3</b> ( <b>1 1 /</b>                                    |        |

| 6                                                                                                  | 6.4.11                                                                                                                                                | INT3 Selection Enable Register 2 (EXT3_INT_SEL2)           | 87     |

|                                                                                                    | 5.4.12                                                                                                                                                | <b>3</b> ( <b>1 1 /</b>                                    |        |

|                                                                                                    | 5.4.13                                                                                                                                                | <b>3</b> ( <b>1 1</b> <i>i</i>                             |        |

|                                                                                                    | 2 1 1 1                                                                                                                                               | External Interrupt Palarity Control Pagister (EVT INT CON) | 00     |

| 6                                                                                                  |                                                                                                                                                       | External Interrupt Polarity Control Register (EXT_INT_CON) |        |

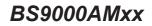

| 6.5                                                                                                |                                                                                                                                                       | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5                                                                                                | Ex                                                                                                                                                    |                                                            | 89     |

| 6.5<br>7                                                                                           | Ex<br>TIME                                                                                                                                            | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  | 89<br> |

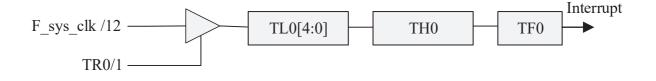

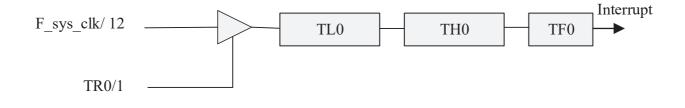

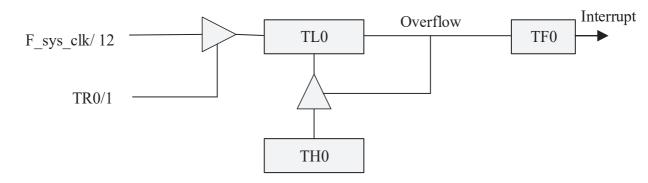

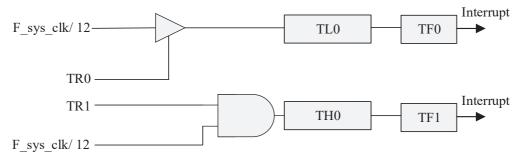

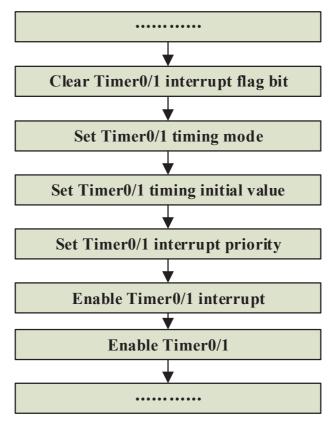

| 6.5<br><b>7</b><br>7.1                                                                             | Б Ех<br><b>ТІМЕ</b><br>ТІМ                                                                                                                            | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7                                                                                           | Ex<br><b>TIME</b><br>TIN<br>TIN                                                                                                                       | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3                                                                      | Ex<br><b>TIME</b><br>TIN<br>TIN                                                                                                                       | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7                                                                 | Ex<br><b>TIME</b><br>TIM<br>TIM<br>TIM                                                                                                                | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7                                                                 | Ex<br>TIME<br>TIM<br>TIM<br>TIM<br>7.3.1<br>7.3.2                                                                                                     | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7.4                                                          | Ex<br>TIME<br>TIM<br>TIM<br>TIM<br>7.3.1<br>7.3.2                                                                                                     | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7                                                | EX<br>TIME<br>TIM<br>TIM<br>TIM<br>7.3.1<br>7.3.2<br>TIM                                                                                              | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7<br>7                                           | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2                                                                                   | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7<br>7                                           | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2<br>PVVM                                                                           | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7<br>8<br>8<br>8.1                               | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2<br>PVVM                                                                           | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7<br>8<br>8<br>8.1<br>8                          | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2<br>PWM<br>16-                                                                     | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7.4<br>7<br>8<br>8<br>8.1<br>8                          | EX<br>TIME<br>TIM<br>TIM<br>7.3.1<br>7.3.2<br>TIM<br>7.4.1<br>7.4.2<br>PVVM<br>16-<br>3.1.1                                                           | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7.4<br>7<br>8<br>8.1<br>8<br>8.1<br>8                        | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2<br>PVVM<br>16-<br>3.1.1<br>3.1.2                                                  | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7<br>7<br>7<br>8<br>8<br>8.1<br>8<br>8<br>8.1<br>8<br>8 | EX<br>TIME<br>TIN<br>TIN<br>7.3.1<br>7.3.2<br>TIN<br>7.4.1<br>7.4.2<br>PWM<br>16-<br>3.1.1<br>3.1.2<br>3.1.3                                          | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

| 6.5<br>7<br>7.1<br>7.2<br>7.3<br>7<br>7<br>7<br>7<br>7<br>8<br>8<br>8.1<br>8<br>8<br>8.1<br>8<br>8 | EX<br>TIME<br>TIM<br>TIM<br>TIM<br>TIM<br>7.3.1<br>7.3.2<br>TIM<br>7.4.1<br>7.4.1<br>7.4.2<br>PWM<br>16-<br>3.1.1<br>3.1.2<br>3.1.3<br>3.1.4<br>3.1.5 | TERNAL INTERRUPT CONFIGURATION PROCEDURES                  |        |

BYD

### BS9000AM Series V1.0

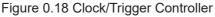

|    | 8.2.2   | Time Base Unit                                                |     |

|----|---------|---------------------------------------------------------------|-----|

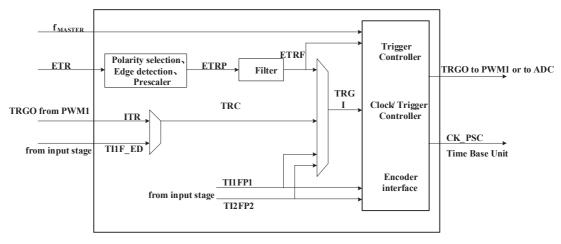

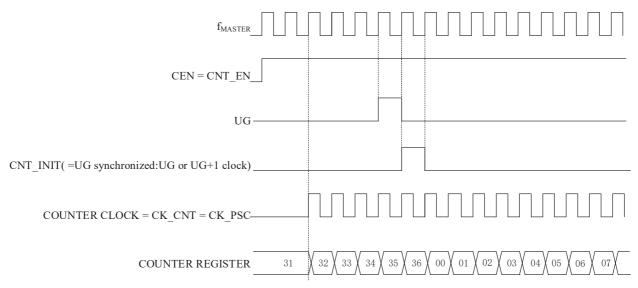

|    | 8.2.3   | Clock/Trigger Controller                                      | 163 |

|    | 8.2.4   | Capture/Compare Channels                                      |     |

|    | 8.2.5   | Interrupt                                                     |     |

| 8  | 8.3 PW  | /M Registers                                                  | 176 |

|    | 8.3.1   | PWM0 Registers                                                | 176 |

|    | 8.3.2   | PWM1 Registers                                                | 214 |

|    | 8.3.3   | PWM0/1 Registers                                              | 234 |

| 8  | 8.4 PW  | M Configuration Procedures                                    | 237 |

|    | 8.4.1   | PWM0 Register Configuration Procedures                        | 237 |

|    | 8.4.2   | PWM1 Register Configuration Procedures                        | 238 |

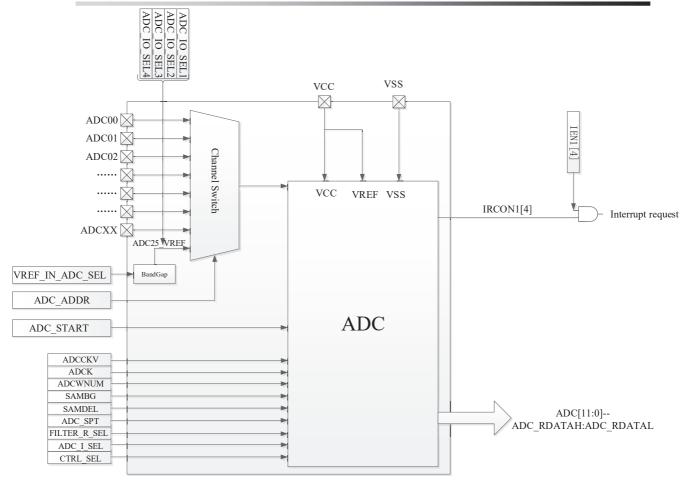

| 9  | ADC.    |                                                               | 240 |

| g  | ).1 Int | RODUCTION                                                     | 240 |

| g  | ).2 AD  | C REGISTERS                                                   | 243 |

|    | 9.2.1   | Module Switch Control Register (PD_ANA)                       | 243 |

|    | 9.2.2   | ADC Scan Control Register (ADC_CH_CFG)                        | 243 |

|    | 9.2.3   | ADC Scan Result Register Low 8 bits (ADC_RDATAL)              | 244 |

|    | 9.2.4   | ADC Scan Result Register High 4 bits (ADC_RDATAH)             | 245 |

|    | 9.2.5   | ADC Sampling Time Configuration Register (ADC_SPT)            | 245 |

|    | 9.2.6   | ADC Sampling Timing Control Register 2 (ADC_ANA_CFG2)         | 245 |

|    | 9.2.7   | ADC Sampling Timing Control Register 1 (ADC_ANA_CFG1)         | 246 |

|    | 9.2.8   | ADC Clock Control Register (ADCCKC)                           | 246 |

|    | 9.2.9   | ADC Pin Control register 1 (ADC_IO_SEL1)                      | 247 |

|    | 9.2.10  | ADC Pin Control register 2 (ADC_IO_SEL2)                      | 248 |

|    | 9.2.11  | ADC Pin Control register 3 (ADC_IO_SEL3)                      | 248 |

|    | 9.2.12  | ADC Pin Control Register 4 (ADC_IO_SEL4)                      | 249 |

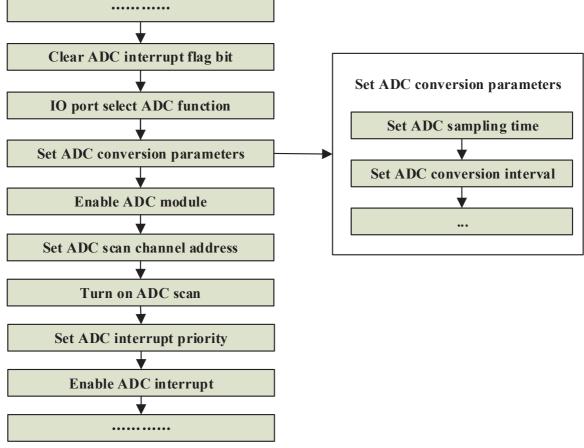

| g  | 9.3 AD  | C CONFIGURATION PROCEDURES                                    | 249 |

| 10 | TOU     | CHKEY                                                         | 252 |

| 1  | 0.1 IN  | TRODUCTION                                                    | 252 |

| 1  | 0.2 To  | DUCHKEY REGISTER                                              | 253 |

|    | 10.2.1  | Module Switch Control Register (PD_ANA)                       |     |

|    | 10.2.2  | CSD Start Scanning Register (CSD_START)                       |     |

|    | 10.2.3  | Touch Channel Control Register (SNS_CH_CFG)                   |     |

|    | 10.2.4  | CSD Pull-up Current Source Selection Register (PULL_I_SELA_L) |     |

|    | 10.2.5  | CSD Count Value Low 8 bits (CSD_RAWDATAL)                     |     |

|    | 10.2.6  | CSD Count Value High 8 bits (CSD_RAWDATAH)                    |     |

|    | 10.2.7  | SNS Channel Selection Register 1 (SNS_IO_SEL1)                |     |

|    | 10.2.8  | SNS Channel Selection Register 2 (SNS_IO_SEL2)                |     |

|    | 10.2.9  | SNS Channel Selection Register 3 (SNS_IO_SEL3)                | 257 |

|    | 10.2.1  | 0 SNS Channel Selection Register 4 (SNS_IO_SEL4)              |     |

### BS9000AM Series V1.0

|    |         | General-purpose MCU with EEPROM, 12bit-ADC, L                  | IN Communication |

|----|---------|----------------------------------------------------------------|------------------|

|    | 10.2.11 | TouchKey Scan Configuration Register 1 (SNS_SCAN_CFG1)         |                  |

|    | 10.2.12 | TouchKey Scan Configuration Register 2 (SNS_SCAN_CFG2)         |                  |

|    | 10.2.13 | TouchKey Scan Configuration Register (SNS_ANA_CFG)             |                  |

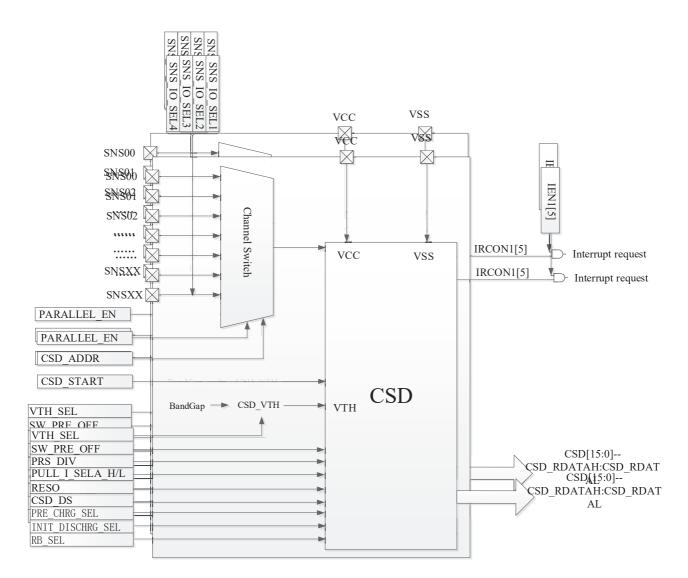

| 10 | 0.3 To  | UCHKEY CONFIGURATION PROCESS                                   |                  |

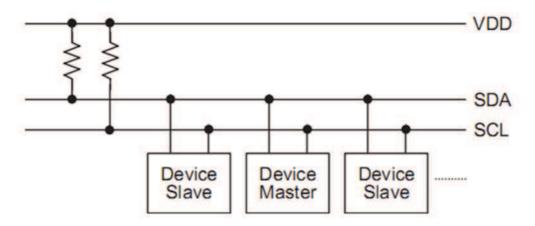

| 11 | IIC     |                                                                |                  |

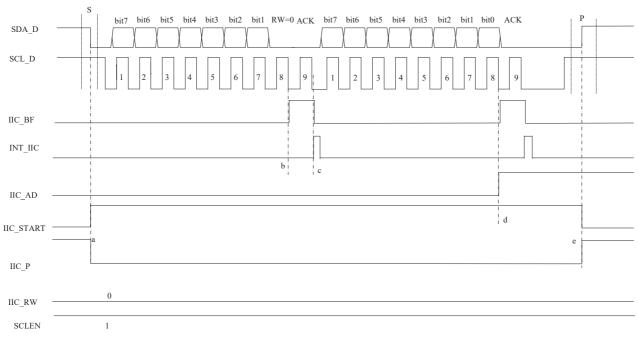

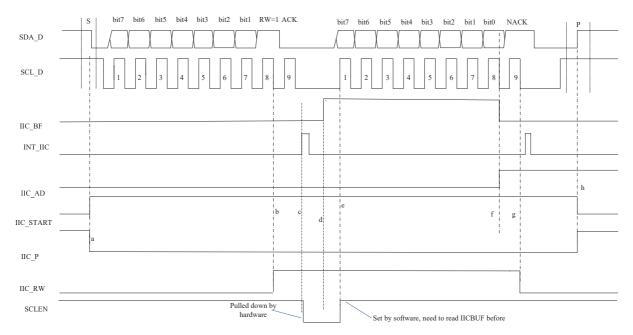

| 1  | 1.1 Cc  | MMUNICATION SEQUENCE                                           |                  |

|    | 11.1.1  | IIC Host Write Sequence                                        |                  |

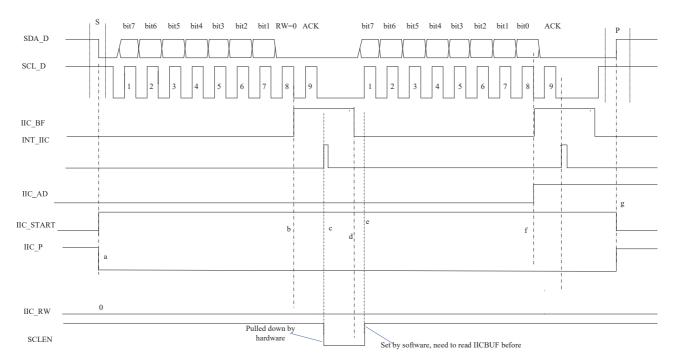

|    | 11.1.2  | IIC Host Write Pull-down Sequence                              |                  |

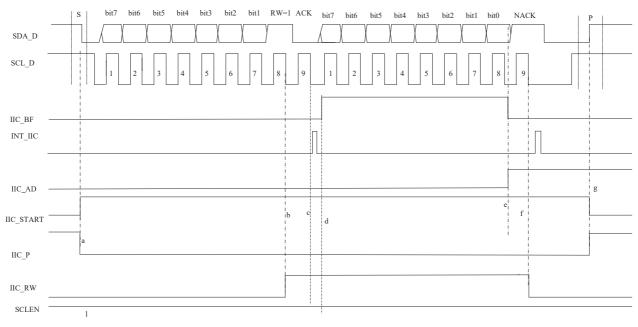

|    | 11.1.3  | IIC Host Read Sequence                                         |                  |

|    | 11.1.4  | IIC Host Read Pull-down Sequence                               |                  |

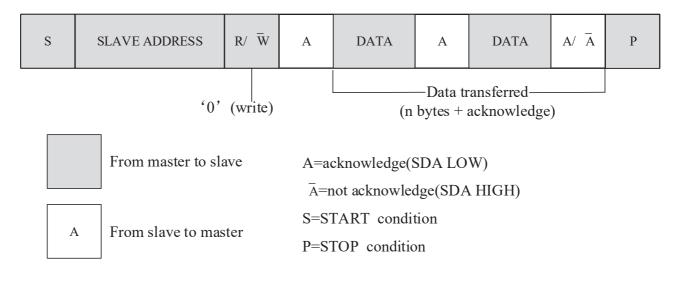

|    | 11.1.5  | IIC Host Write Data                                            |                  |

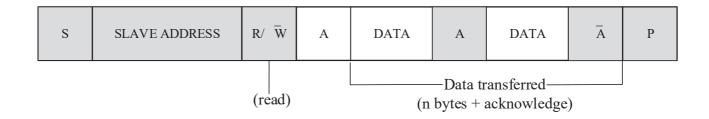

|    | 11.1.6  | IIC Host Read Data                                             |                  |

| 1' | 1.2 IIC | REGISTERS                                                      |                  |

|    | 11.2.1  | IIC Address Register (IICADD)                                  |                  |

|    | 11.2.2  | IIC Status Register (IICSTAT)                                  |                  |

|    | 11.2.3  | IIC Transmit/Receive Data Register (IICBUF)                    |                  |

|    | 11.2.4  | IIC Status Register (IICCON)                                   | 273              |

|    | 11.2.5  | IIC Transmit/Receive Buffer Register (IICBUFFER)               |                  |

|    | 11.2.6  | IIC IO Configuration Register (IIC_IO_SEL)                     | 276              |

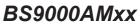

| 1  | 1.3 IIC | CONFIGURATION PROCEDURE                                        | 278              |

| 12 | SPI     |                                                                | 279              |

| 1: | 2.1 Fu  | NCTIONS                                                        |                  |

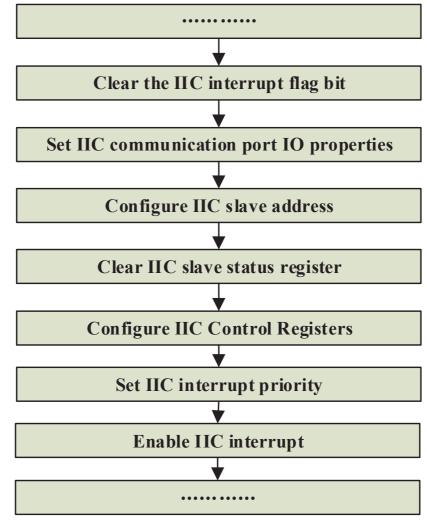

| 1  | 2.2 Co  | MMUNICATION SEQUENCE                                           |                  |

| 1  | 2.3 SF  | I Registers                                                    |                  |

|    | 12.3.1  | SPI Configuration Register 1 (SPI_CFG1)                        |                  |

|    | 12.3.2  | SPI Configuration Register 2 (SPI_CFG2)                        |                  |

|    | 12.3.3  | SPI Status Register (SPI_STATE)                                |                  |

|    | 12.3.4  | SPI Data Register (SPI_SPID)                                   |                  |

|    | 12.3.5  | SPI Transmit Buffer Start Address Register (SPI_TX_START_ADDR) |                  |

|    | 12.3.6  | SPI Receive Buffer Start Address Register (SPI_RX_START_ADDR)  |                  |

|    | 12.3.7  | SPI Data Buffer Address Number Low 8-bit Register (SPI_NUM_L)  |                  |

|    | 12.3.8  | SPI Data Buffer Address Number High 3-bit Register (SPI_NUM_H) |                  |

|    | 12.3.9  | SPI Host Mode Receiver Clock Selection Register (SPI_MCLK_MOD) |                  |

|    | 12.3.10 | SPI IO High Speed Mode Enable Register (SPI_SPEED_EN)          |                  |

|    | 12.3.11 | SPI IO Selection Register (SPI_IO_SEL)                         |                  |

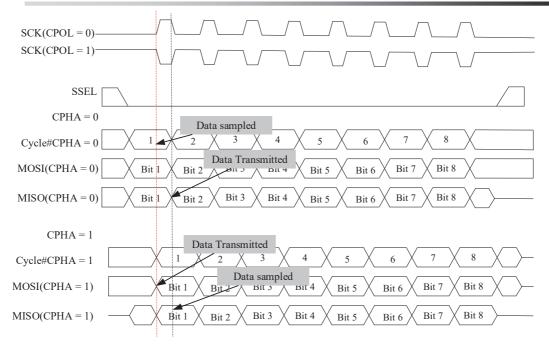

| 1: | 2.4 SF  | I CONFIGURATION PROCEDURE                                      |                  |

| 13 | UAR     | Τ                                                              |                  |

| 1; | 3.1 De  | SCRIPTION                                                      |                  |

|    | 13.1.1  | Baud Rate Generation                                           |                  |

### BS9000AM Series V1.0

| 13.1.2  | Functions of Emitter                          | 290 |

|---------|-----------------------------------------------|-----|

| 13.1.3  | Functions of Receiver                         | 291 |

| 13.1.4  | Receiver Sampling Method                      |     |

| 13.1.5  | Multi-processor Mode                          | 292 |

| 13.2 UA | RT REGISTER                                   | 293 |

| 13.2.1  | UART Control Register 1 (UART_CON1)           | 293 |

| 13.2.2  | UART Control Register 2 (UART_CON2)           | 294 |

| 13.2.3  | UART Status Flag Register (UART_STATE)        | 294 |

| 13.2.4  | UART Data Register (UART_BUF)                 | 295 |

| 13.2.5  | UART Baud Rate Control Register (UART_BDL)    | 296 |

| 13.2.6  | UART Clock Selection Register (UART_CLK_SEL)  | 296 |

| 13.2.7  | UART IO Selection Register (UART_IO_SEL)      | 296 |

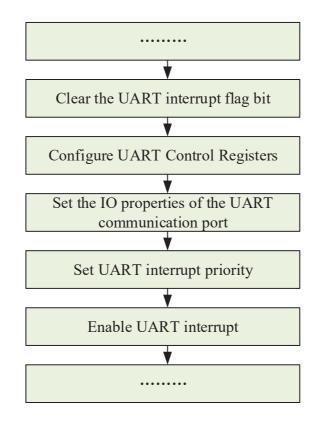

| 13.3 UA | RT CONFIGURATION PROCEDURE                    | 297 |

| 14 SCI  |                                               | 299 |

|         |                                               |     |

|         |                                               |     |

|         | UART Mode                                     |     |

|         | LIN Frame Mode                                |     |

|         | UD RATE GENERATION                            |     |

|         | ITTER FUNCTION                                |     |

|         | CEIVER FUNCTION                               |     |

|         | Receiver Sampling Method                      |     |

|         | Receiver Wakeup from Sleep                    |     |

|         | I CONNECTION MODE                             |     |

|         | W POWER WAKE-UP                               |     |

|         | AME MODE                                      |     |

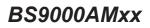

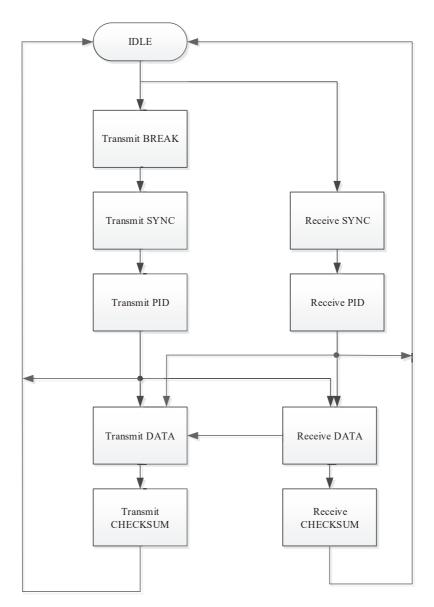

|         | Frame Format                                  |     |

|         | LIN Communication                             |     |

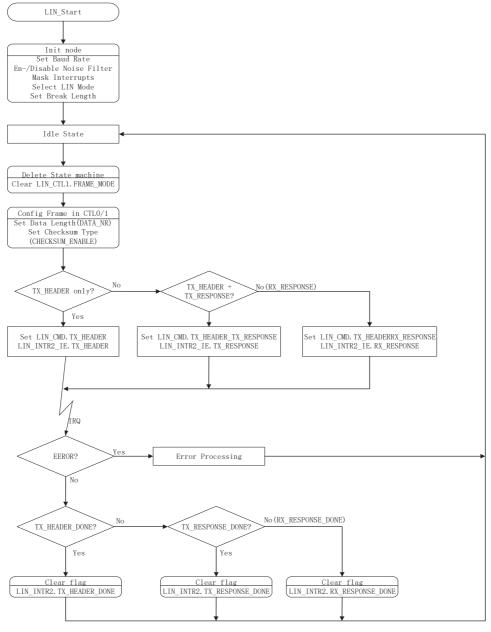

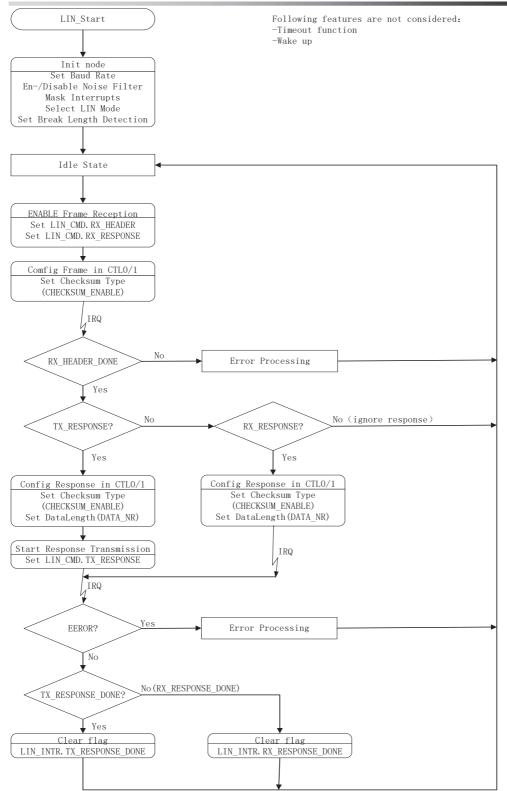

|         | LIN Software Flow Chart                       |     |

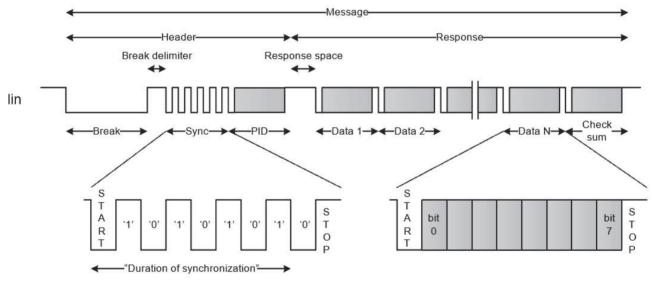

|         | AME MODE STATE MACHINE                        |     |

|         | TRUCTIONS FOR INTERRUPT HANDLING              |     |

|         |                                               |     |

| 14.10.1 |                                               |     |

| 14.10.2 |                                               |     |

|         | Baud Rate Control Low 8-bit Register(SCI_BDL) |     |

|         | Control Register 1 (SCI_C1)                   |     |

|         | Control Register 2 (SCI_C2)                   |     |

|         | Control Register 3 (SCI_C3)                   |     |

|         | Sync Segment Control Register (SCI_S2)        |     |

| 14.10.8 |                                               |     |

|         | SCI Data Register (SCI_D)                     |     |

| 14.10.1 | 0 SCI Interrupt Clear Register (SCI_INT_CLR)  |     |

### BS9000AM Series V1.0

|            |        | DOGOCOAM Series V                                                               |      |

|------------|--------|---------------------------------------------------------------------------------|------|

|            | _      | General-purpose MCU with EEPROM, 12bit-ADC, LIN Communicat                      | tion |

| 14         | .10.11 | LIN Frame Timeout Configuration Register (LIN_FRAME_TIMEOUT)                    | 327  |

| 14         | .10.12 | LIN Configuration Register 1 (LIN_CTL1)                                         | 328  |

| 14         | .10.13 | LIN Configuration Register 0 (LIN_CTL0)                                         | 329  |

| 14         | .10.14 | LIN Transfer Command Register (LIN_LIN_CMD)                                     | 330  |

| 14         | .10.15 | LIN Synchronization Section Baud Rate Count Period Register (LIN_SYNC_CO UNTER) | 332  |

| 14         | .10.16 | LIN Status Register (LIN_STATUS)                                                |      |

| 14         | .10.17 | LIN Data Field Count Value Register (LIN_DATA_IDX)                              | 333  |

| 14         | .10.18 | LIN Interrupt Status Register 1 (LIN_INTR1)                                     | 335  |

| 14         | .10.19 | LIN Interrupt Status Register 2 (LIN_INTR2)                                     |      |

| 14         | .10.20 | LIN Interrupt Enable Register 1 (LIN_INTR1_IE)                                  | 337  |

| 14         | .10.21 | LIN Interrupt Enable Register 2 (LIN_INTR2_IE)                                  |      |

|            | .10.22 | LIN Transmit Register Description                                               |      |

| 14         | .10.23 | LIN Receive Register Description                                                | 340  |

| 15         | PROGR  | AMMING AND DEBUGGING                                                            | .342 |

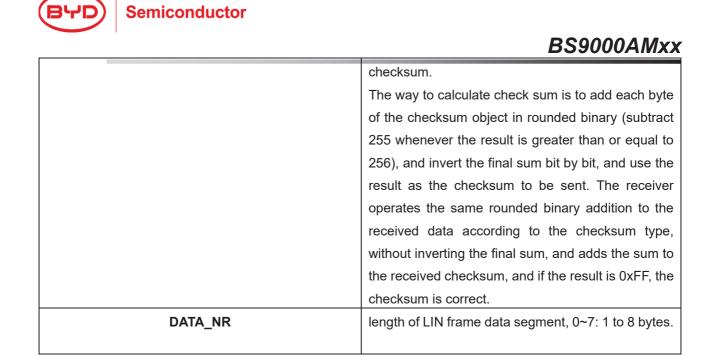

| 15.1       | SWE    | CIRCUIT CONNECTION                                                              | .342 |

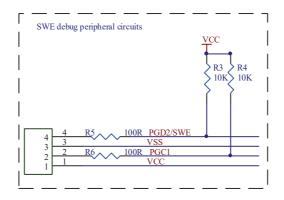

| 15.2       | Сара   | CITIVE TOUCHKEY DATA ASSISTED PROGRAMMING & DEBUGGING                           | .342 |

| 16         | CPU IN | STRUCTIONAL SYSTEM                                                              | 344  |

| 16.1       | INSTR  | UCTION CODE                                                                     | .344 |

| 16.2       | INSTR  | UCTION SET                                                                      | .344 |

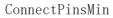

| 17         | APPLIC | ATION CIRCUIT FOR REFERENCE                                                     | .351 |

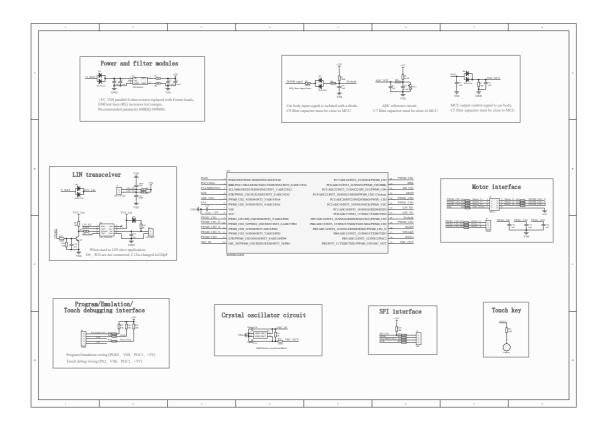

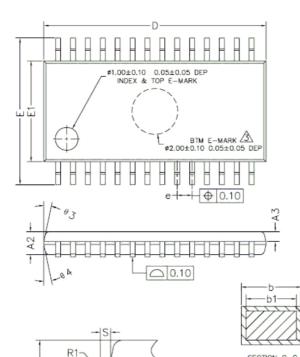

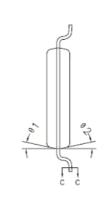

| 18         | ΡΔΩΚΔ  | GE INFORMATION                                                                  | 352  |

| -          |        |                                                                                 |      |

| 18.1       | - •    | 20                                                                              |      |

| 18.2       | TSSC   | DP28                                                                            | 353  |

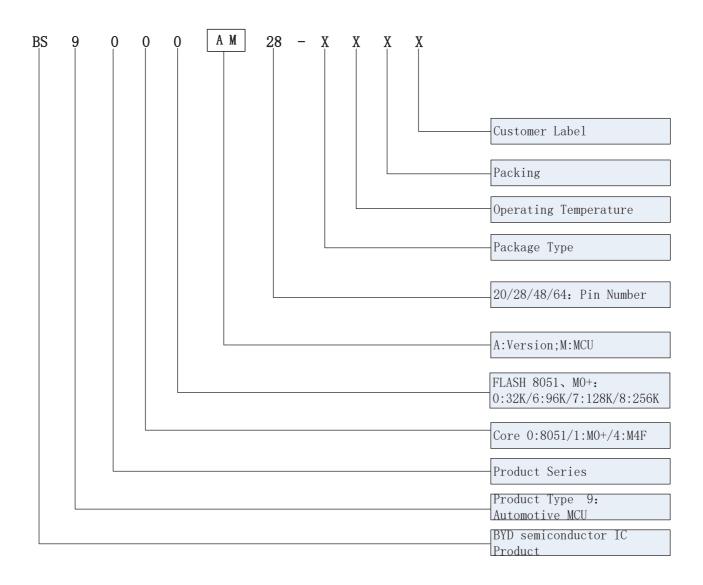

| 19         | ORDER  |                                                                                 | 354  |

| 20         | REVISI | ON HISTORY                                                                      | .355 |

| 21         |        |                                                                                 | 356  |

| <b>∠ I</b> | DISCLA |                                                                                 | 330  |

|            |        |                                                                                 |      |

### BS9000AM Series V1.0

General-purpose MCU with EEPROM, 12bit-ADC, LIN Communication

#### **BS9000AM Series MCU Overview** 1

#### 1.1 **Features**

- Core: High-speed 8051, 1T Instruction cycle

- Operating Frequency: 24MHz /16MHz /12MHz/8MHz

- Clock Offset: ±1% @-20°C~65°C, 5V or 0 ±3% @-40°C ~125°C, 5V

- Memories

- 30.5KBytes FLASH 0

- 1024Bytes EEPROM 0

- 256 Bytes(idata)+2048 Bytes(xdata) SRAM

- Support IAP online update, memories protection

- Clock Source, Reset and Power Management

- o Internal Low-speed RC: 32768Hz, clock offset within ±3%@25°C, 5V or ±5% @-

- 40°C ~125°C, 5V

- Internal High-speed OSC: 1MHz

- External OSC: 16MHz/12MHz/8MHz 0

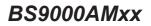

- o 7 Reset modes, among which the BOR mode is ON with the voltage selectable 2.6V/2.8V/3.7V/4.2V

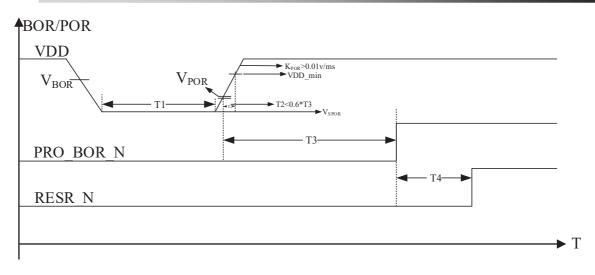

- Low voltage detection: 3V/3.3V/3.6V/3.9V/4.5V

- 10

- 10k Embedded Pull-up/ Pull-down  $\cap$ Resistors

- Provide multiplexing of Peripheral 0 functions

- I/O Lines with External Interrupt Capability, INT0 to 2 enable Rising Edge, Falling Edge or both interrupt respectively, INT3 enables both rising and falling interrupt.

- Communications

- UART

- o IIC slave communication supporting 100/400kHz

- SPI: master with a frequency up to 4M and 2M slave

- SCI: LIN2.1 protocol, up to 115200bps Baud

- 16-bit PWM

- PWM0 supports 4-channel input/output with 3-channel complementary output

- PWM1 supports 3-channel input/output

- Operating voltage: 3.0V to 5.5V, 3.3V or 5.0V typ

- Operating temperature: -40°C to 125°C

- High accuracy 12-bit ADC

- Up to 24 Analog Input channels

- 2.048V/4.096V internal reference voltage detection

- Interrupt

- High/Low-Level Interrupt Selection

- ADC, CSD, INT0/1/2/3, LVDT, Timer0/1/2, RTC, WDT, UART, SCI, IIC, SPI

- Timer

- 3 16-bit Timer0/1/2 0

- 16-bit RTC, wake-up in low-power mode

- Watchdog Timer

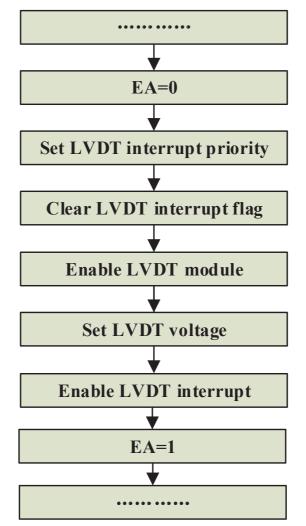

- Low-power Mode

- Wait Mode

- Sleep Mode, 20µA @5V typ consumption 0

- TouchKey

- The sensitivity of each key can be set individually

- o Capacitive TouchKey can be multiplexed with GPIO lines

- 2-wire programming and single-wire debugging emulator IO

- Packages: QFN20/TSSOP28

#### 1.2 Description

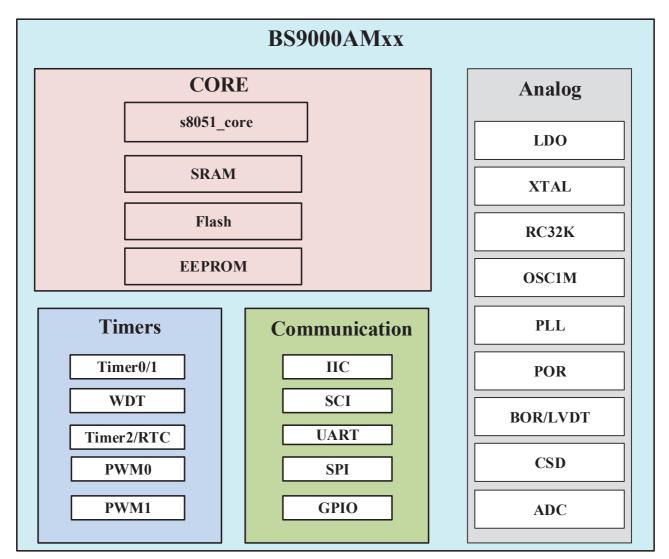

BS9000AM series are 8-bit general-purpose microcontrollers that meets the quality requirements of AECQ0-100 Grade 1. Based on 8051 CORE and 1T instruction cycle, it runs faster than the Standard 8051 with 12T. Also, it is compatible with Standard 8051 instructions.

The peripherals of BS9000AM series devices includes WDT, PWM0/1, Timer0, Timer1, Timer2, RTC, IIC, SPI, UART, SCI with Lin2.1 protocol, LV Detection, BOR, 12-bit successive-approximation ADC, Touch-key Detection and Low-power mode. The memory supports EEPROM real-time data storage. The BS9000AM series are available in QFN20 and TSSOP28 packages. The BS9000AMxx is suitable for many applications such as end actuator unit, end sensor detection control.

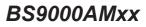

### 1.3 System Block Diagram

Figure 0.1 BS9000AMxx Block Diagram

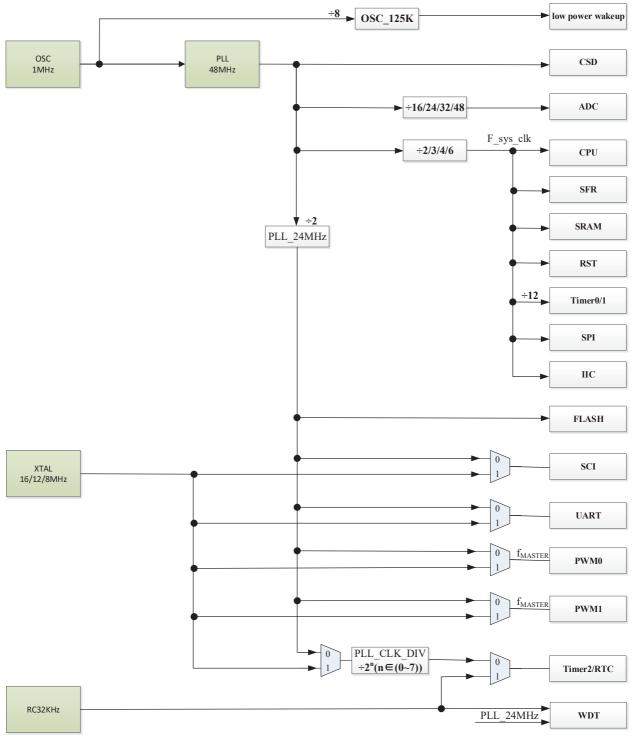

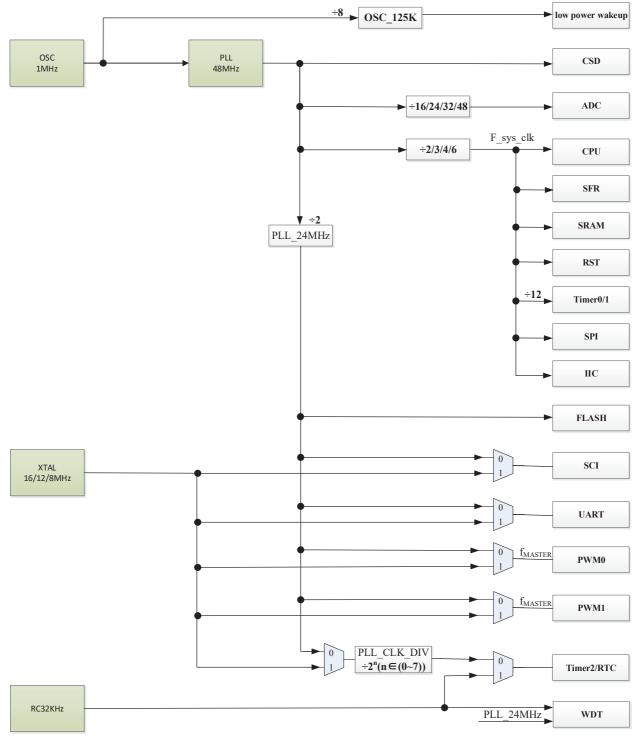

### 1.4 Clock Diagram

#### **Main Clock**

- OSC\_125KHz: a timer clock used in Low-consumption Wakeup Interrupt Mode.

- F\_sys\_clk: select clock frequency of 24MHz/16MHz/12MHz/8MHz.

Semiconductor

- f<sub>MASTER:</sub> PWM PLL\_24MHz/XTAL can be selected.

- PLL\_24MHz: a clock for FLASH program and read, SCI/UART/PWM0/PWM1.

- XTAL: External Crystal. When the frequency is at 16M or 12M or 8M, it acts as a timer for Timer2/RTC, also a clock SCI/UART/ PWM0/PWM1.

- RC32KHz: The frequency is 32768Hz, used for Timer2, RTC and WDT setting.

#### 1.5 Selection Table

| P/N               | BS9000AM20-QBBX | BS9000AM28-TBBX |

|-------------------|-----------------|-----------------|

| Operating Voltage | 3.0V to 5.5V    | 3.0V to 5.5V    |

| Core              | 1T 8051         | 1T 8051         |

| Operating         |                 |                 |

| Frequency         | 24M             | 24M             |

| FLASH (Byte)      | 30.5K           | 30.5K           |

| SRAM (Byte)       | 256+2048        | 256+2048        |

| EEPROM (Byte)     | 1024            | 1024            |

| GPIO              | 18              | 26              |

| ADC               | 16              | 24              |

| KEY               | 16              | 24              |

| Timer             | 4               | 4               |

| PWM0              | 4ch             | 4ch             |

| PWM1              | 3ch             | 3ch             |

| SPI               | 1               | 1               |

| INT               | 18              | 26              |

| IIC               | 1               | 1               |

| UART              | 1               | 1               |

| SCI               | 1               | 1               |

| Package           | QFN20           | TSSOP28         |

Table 0.3 Selection Table

#### **1.6 Pin configuration**

#### 1.6.1 QFN20

Figure 0.4 BS9000AM20-QBBX Package and Pinout Drawing

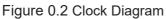

#### 1.6.2 TSSOP28

Figure 0.5 BS9000AM28-TBBX Package and Pinout Drawing

### **1.7 Pin Functions**

| BS9000AM20-xxxx | BS9000AM28-xxxx | Function                                                                                                                                                                                                                                                                                                                                 |  |

|-----------------|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 19              | 1               | By Default: GPIO <pa0><br/>Other functions: ADC00: ADC channel 0<br/>INT0: External Interrupt 0<br/>PGD1: Programming Interface<br/>PGD2: Programming Interface<br/>SWE: Single Wire Emulation IO<br/>SNS0: TouchKey channel 0</pa0>                                                                                                     |  |

| 20              | 2               | By Default: GPIO <pa1><br/>Other functions: ADC01: ADC channel 1<br/>INT3_0: External Interrupt 3_0<br/>TXD0: Transmit Serial Data<br/>TXD1: Transmit Serial Data<br/>MOSI: Master Out Slave In in SPI Master Mode<br/>SDA: IIC serial data line<br/>PGC1: Programming Interface<br/>BRK: Break input<br/>SNS1: TouchKey channel 1</pa1> |  |

| 1               | 3               | By Default: GPIO <pa2><br/>Other functions: ADC02: ADC channel 2<br/>INT3_1: External Interrupt 3_1<br/>RXD0: Receive Serial Data<br/>RXD1: Receive Serial Data<br/>MISO: Master In Slave Out (MISO) in SPI Master mode<br/>SCL: IIC serial clock line<br/>SNS2: TouchKey channel 2</pa2>                                                |  |

| 2               | 4               | By Default: GPIO <pa3><br/>Other functions: ADC03: ADC channel 3<br/>INT3_2: External Interrupt 3_2<br/>SCK: SPI clock line<br/>PWM1_CH1: PWM1 channel<br/>ETR: External interrupt<br/>SNS3: TouchKey channel 3</pa3>                                                                                                                    |  |

#### BS9000AMxx

|   |    | DS9000AIVIXX                                  |

|---|----|-----------------------------------------------|

|   |    | By default: GPIO <pa4></pa4>                  |

|   |    | Other functions: ADC04: ADC channel 4         |

|   | 5  | INT3_3: External interrupt 3_3                |

|   |    | PWM0_CH1_N: PWM0 complementary output channel |

|   |    | SNS4: TouchKey channel 4                      |

|   |    | By default: GPIO <pa5></pa5>                  |

|   |    | Other functions: ADC05: ADC channel 5         |

|   | 6  | INT3_4: external interrupt 3_4                |

|   |    | PWM0_CH2_N: PWM0 complementary output channel |

|   |    | SNS5: TouchKey channel 5                      |

| 3 | 7  | By default: Ground <vss></vss>                |

| 4 | 8  | By default: Power Supply <vcc></vcc>          |

|   |    | By default: GPIO <pd0></pd0>                  |

|   |    | Other functions: ADC6: ADC channel 6          |

| 5 | 9  | INT3_5: external interrupt 3_5                |

| 5 | 9  | SPI_CS0: SPI chip select signal               |

|   |    | PWM1_CH1: PWM1 channel                        |

|   |    | SNS6: TouchKey channel 6                      |

|   |    | By default: GPIO <pd1></pd1>                  |

|   | 10 | Other functions: ADC7: ADC channel 7          |

| 6 |    | INT3_6: external interrupt 3_6                |

| 0 |    | PWM1_CH1: PWM 1channel                        |

|   |    | PWM0_CH1_N: PWM0 complementary output channel |

|   |    | SNS7: TouchKey channel 7                      |

|   |    | By default: GPIO <pd2></pd2>                  |

|   |    | Other functions: ADC8: ADC channel 8          |

| 7 | 11 | INT1: external interrupt 1                    |

|   |    | PWM0_CH1_N: PWM0 complementary output channel |

|   |    | SNS8: TouchKey channel 8                      |

|   |    | By default: GPIO <pd3></pd3>                  |

|   |    | Other functions: ADC9: ADC channel 9          |

| 8 | 12 | INT3_7: external interrupt 3_7                |

|   |    | PWM0_CH2_N: PWM0 complementary output channel |

|   |    | SNS9: TouchKey channel 9                      |

|   |    | By default: GPIO <pd4></pd4>                  |

|   |    | Other functions: ADC10: ADC channel 10        |

| 9 | 13 | INT3_8: external interrupt 3_8                |

| 9 | 15 | PWM0_CH2: PWM0 channel                        |

|   |    | ETR: external interrupt                       |

|   |    | SNS10: TouchKey channel 10                    |

|   |    |                                               |

|    |    | By default: GPIO <pb0></pb0>                      |

|----|----|---------------------------------------------------|

|    |    | Other functions: ADC11: ADC channel 11            |

| 10 |    | INT3 9: external interrupt 3 9                    |

| 10 |    | PWM0_CH1: PWM0 channel                            |

|    |    | BRK: Break output                                 |

|    |    | SNS11: TouchKey channel 11                        |

|    |    | By default: GPIO <pb1></pb1>                      |

|    |    | Other functions: INT3 10: external interrupt 3 10 |

|    | 14 | RXD0: Receive Serial Data                         |

| 11 |    | RXD1: Receive Serial Data                         |

|    |    | PWM0 CH1: PWM0 channel                            |

|    |    | OSC_IN: external oscillator input                 |

|    |    | By default: GPIO <pb2></pb2>                      |

|    |    | Other functions: INT3_11: External interrupt 3_11 |

| 10 | 45 | TXD0: Transmit Serial Data                        |

| 12 | 15 | TXD1: Transmit Serial Data                        |

|    |    | PWM0_CH2: PWM0 channel                            |

|    |    | OSC_OUT: external oscillator output               |

|    |    | By default: GPIO <pb3></pb3>                      |

|    |    | Other functions: ADC12: ADC channel 12            |

|    | 16 | INT3_12: external interrupt 3_12                  |

|    |    | PGC2: programming interface                       |

|    |    | SNS12: TouchKey channel 12                        |

|    |    | By default: GPIO <pb4></pb4>                      |

|    |    | Other functions: ADC13: ADC channel 13            |

|    | 17 | INT3_13: external interrupt 3_13                  |

|    | 17 | TXD0: Transmit Serial Data                        |

|    |    | TXD1: Transmit Serial Data                        |

|    |    | SNS13: TouchKey channel 13                        |

|    |    | By default: GPIO <pb5></pb5>                      |

|    |    | Other functions: ADC14: ADC channel 14            |

|    |    | INT3_14: external interrupt 3_14                  |

|    | 18 | RXD0: Receive Serial Data                         |

|    |    | RXD1: Receive Serial Data                         |

|    |    | PWM0_CH1_N: PWM complementary output channel      |

|    |    | SNS14: TouchKey channel 14                        |

|    |    | By default: GPIO <pb6></pb6>                      |

|    |    | Other functions: ADC15: ADC channel 15            |

| 13 | 19 | INT3_15: external interrupt 3_15                  |

|    |    | TXD0: Transmit Serial Data                        |

|    |    | TXD1: Transmit Serial Data                        |

|    |     | SDA: IIC serial data line                           |

|----|-----|-----------------------------------------------------|

|    |     | PWM0_CH1: PWM0 channel                              |

|    |     | SNS15: TouchKey channel 15                          |

|    |     | By default: GPIO <pb7></pb7>                        |

|    |     | Other functions: ADC16: ADC channel 16              |

|    |     | INT3_16: external interrupt 3_16                    |

| 14 | 20  | RXD0: Receive Serial Data                           |

| 14 | 20  | RXD1: Receive Serial Data                           |

|    |     | SCL: IIC serial clock line                          |

|    |     | PWM0_CH1: PWM0 channel                              |

|    |     | SNS16: TouchKey channel 16                          |

|    |     | By default: GPIO <pc0></pc0>                        |

|    |     | Other functions: ADC17: ADC channel 17              |

|    | 21  | INT3_17: external channel 3_17                      |

|    | 21  | TXD0: Transmit Serial Data                          |

|    |     | TXD1: Transmit Serial Data                          |

|    |     | SNS17: TouchKey channel 17                          |

|    |     | By default: GPIO <pc1></pc1>                        |

|    |     | Other functions: ADC18: ADC channel 18              |

|    | 22  | INT3_18: external interrupt 3_18                    |

|    | ~~~ | RXD0: Receive Serial Data                           |

|    |     | RXD1: Receive Serial Data                           |

|    |     | SNS18: Touch key channel 18                         |

|    |     | By default: GPIO <pc2></pc2>                        |

|    |     | Other functions: ADC19: ADC channel 19              |

| 15 | 23  | INT3_19: external interrupt 3_19                    |

|    |     | SCK: SPI serial clock line                          |

|    |     | PWM1_CH1: PWM1 channel                              |

|    |     | SNS19: TouchKey channel 19                          |

|    |     | By default: GPIO <pc3></pc3>                        |

|    |     | Other functions: ADC20: ADC channel 20              |

| 16 | 24  | INT2: external interrupt 2                          |

|    |     | MISO: Master In Slave Out (MISO) in SPI Master mode |

|    |     | PWM1_CH2: PWM1 channel                              |

|    |     | SNS20: TouchKey channel 20                          |

|    |     | By default: GPIO <pc4></pc4>                        |

|    |     | Other functions: ADC21: ADC channel 21              |

| 17 | 25  | INT3_20: external interrupt 3_20                    |

|    |     | MOSI: Master Out Slave In in SPI Master Mode        |

|    |     | PWM0_CH2: PWM0 channel                              |

|    |     | SNS21: TouchKey channel 21                          |

|    |    | By default: GPIO <pc5></pc5>           |  |  |  |  |  |

|----|----|----------------------------------------|--|--|--|--|--|

|    |    | Other functions: ADC22: ADC channel 22 |  |  |  |  |  |

| 18 | 26 | INT3_21: external interrupt 3_21       |  |  |  |  |  |

| 10 | 20 | SPI_CS1: chip select                   |  |  |  |  |  |

|    |    | PWM0_CH3: PWM0 channel                 |  |  |  |  |  |

|    |    | SNS22: TouchKey channel 22             |  |  |  |  |  |

|    |    | By default: GPIO <pc6></pc6>           |  |  |  |  |  |

|    |    | Other functions: ADC23: ADC channel 23 |  |  |  |  |  |

|    | 27 | INT3_22: external interrupt 3_22       |  |  |  |  |  |

|    | 21 | PWM0_CH1: PWM0 channel                 |  |  |  |  |  |

|    |    | BRK: break input                       |  |  |  |  |  |

|    |    | SNS23: TouchKey channel 23             |  |  |  |  |  |

|    |    | By default: GPIO <pc7></pc7>           |  |  |  |  |  |

|    |    | Other functions: ADC24: ADC channel 24 |  |  |  |  |  |

|    | 28 | INT3_23: external interrupt 3_23       |  |  |  |  |  |

|    |    | PWM0_CH1: PWM0 channel                 |  |  |  |  |  |

|    |    | SNS24: TouchKey channel 24             |  |  |  |  |  |

|    |    |                                        |  |  |  |  |  |

Table 0.6 PIN MAP

Note : Oscillator uses the OSC\_IN pin to input clock.

# 2 Electrical Characteristics

#### 2.1 AC Characteristics

| Parameter     | Symbol                     | Conditions                   | Clock Skew | Unit |

|---------------|----------------------------|------------------------------|------------|------|

|               |                            | Ta=25℃, @5V                  | ±1%        |      |

| Fundamental   |                            | Ta= -40℃ ~ 85℃, @5V          | ±2%        |      |

|               | OSC1M                      | Ta= -40°C ~ 125°C, @5V       | ±3%        |      |

| frequency     |                            | VCC=3.0V ~ 5.5V, environment | ±3%        |      |

|               |                            | temperature 25°C             | ±3%        |      |

|               |                            | Ta=25℃ @5V                   | ±1%        | MHz  |

|               | F_sys_clk                  | Ta= -40℃ ~ 85℃, @5V          | ±2%        | -    |

| System clock  |                            | Ta= -40°C to 125°C, @5V      | ±3%        |      |

|               |                            | VCC=3.0V ~ 5.5V, environment | ±3%        |      |

|               |                            | temperature 25°C             | ±3%        |      |

|               |                            | Ta=25℃, @5V                  | ±3%        |      |

| Internal low- | w- Ta= -40°C to 125°C, @5V |                              | ±5%        | kHz  |

| speed clock   | RC32k                      | VCC=3.0V ~ 5.5V, environment | 150/       | KITZ |

|               |                            | temperature 25°C             | ±5%        |      |

Table 0.1 AC characteristics

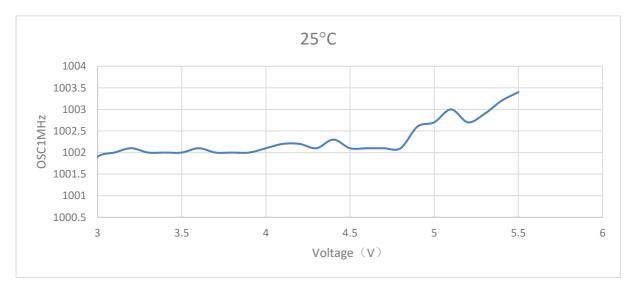

Figure 0.2 OSC1MHz Voltage Curve

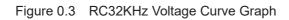

Figure 0.4 OSC1MHz Temperature Curve Graph

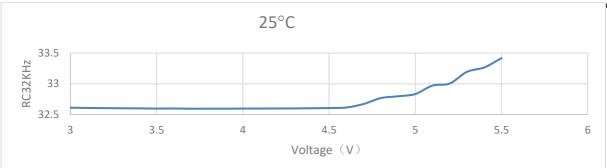

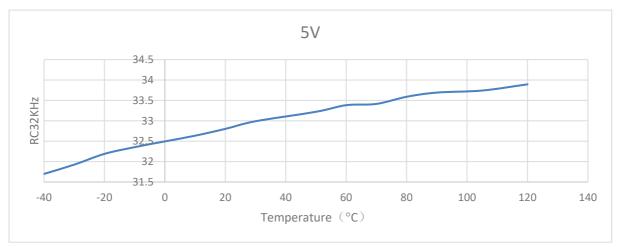

Figure 0.5 RC32KHz Temperature Curve Graph

#### **DC** Characteristics 2.2

#### Table 2.6 DC characteristics (Tamb = $25^{\circ}$ C, unless otherwise specified)

| Parameter | Symbol | Conditions | Min | Тур | Max | Unit |

|-----------|--------|------------|-----|-----|-----|------|

| Operating | VCC    | _          | 3.0 | _   | 5.5 | V    |

| voltage   | 100    |            | 0.0 |     | 0.0 | v    |

#### BS9000AMxx

|                    | -      |                                                                                                        |   |      |   |    |

|--------------------|--------|--------------------------------------------------------------------------------------------------------|---|------|---|----|

|                    |        | @5V, 24M system clock without load, other functions turned off                                         | - | 9.97 |   | mA |

|                    |        | @5V, 16M, system clock without load, other functions turned off                                        | - | 7.40 |   | mA |

|                    |        | @5V, 12M system clock without load, other functions turned off                                         | - | 5.90 |   | mA |

|                    |        | @5V, 8M system clock without load, other functions turned off                                          | - | 4.60 |   | mA |

|                    |        | @3.3V, 24M system clock without load, other functions turned off                                       | - | 9.97 | - | mA |

|                    |        | @3.3V, 16M system clock without load, other functions turned off                                       | - | 7.40 | - | mA |

|                    | Active | @3.3V, 12M system clock without load, other functions turned off                                       | - | 5.90 | - | mA |

|                    |        | @3.3V, 8M system clock without load, other functions turned off                                        | - | 4.57 | - | mA |

|                    |        | @3.0V, 24M system clock without load, other functions turned off                                       |   | 9.97 | - | mA |

|                    |        | @3.0V, 16M system clock without load, other functions turned off                                       | - | 7.40 | - | mA |

| Operating<br>Modes |        | @3.0V, 12M system clock without load, other functions turned off                                       | - | 5.90 | - | uA |

|                    |        | @3.0V, 8M system clock without load, other functions turned off                                        | - | 4.57 | - | uA |

|                    |        | <ul> <li>@5V 24M system clock, IO output low, enter wait mode, other functions turned off</li> </ul>   | _ | 3.73 | - | mA |

|                    |        | @3.3V 24M system clock, IO output low, enter wait mode, other functions turned off                     | - | 3.73 | _ | mA |

|                    |        | <ul> <li>@3.0V 24M system clock, IO output low, enter wait mode, other functions turned off</li> </ul> | - | 3.73 | - | mA |

|                    |        | @5V 16M system clock, IO output low, enter wait mode, other functions turned off                       | - | 3.77 | - | mA |

|                    | Wait   | @3.3V 16M system clock, IO output low, enter wait mode, other functions turned off                     | - | 3.70 | - | mA |

|                    |        | @3.0V 16M system clock, IO output low, enter wait mode, other functions turned off                     | - | 3.70 | - | mA |

|                    |        | @5V 12M system clock, IO output low, enter wait mode, other functions turned off                       | - | 3.77 | - | mA |

|                    |        | @3.3V 12M system clock, IO output low, enter wait mode, other functions turned off                     | - | 3.73 | - | mA |

|                    |        | @3.0V 12M system clock, IO output low, enter wait mode, other functions turned off                     | - | 3.73 | - | mA |

| L                  | 1      | 1                                                                                                      |   |      | 1 |    |

#### BS9000AMxx

|                                     |       | F                                                                                                                            |             |        |         |    |

|-------------------------------------|-------|------------------------------------------------------------------------------------------------------------------------------|-------------|--------|---------|----|

|                                     |       | @5V 8M system clock, IO output low, enter wait mode, other functions turned off                                              | -           | 3.73   | -       | mA |

|                                     |       | @3.3V 8M system clock, IO output low, enter wait                                                                             | -           | 3.70   | -       | mA |

|                                     |       | mode, other functions turned off@3.0V 8M system clock, IO output low, enter wait                                             | _           | 3.67   | -       | mA |

|                                     |       | mode, other functions turned off<br>@5V 24M system clock, PCON = 0x01, IO output                                             |             |        |         |    |

|                                     |       | low,other functions turned off                                                                                               | -           | 21.33  | -       | μA |

|                                     | Sleep | @3.3V 24Msystem clock, PCON = 0x01, IO output<br>low,other functions turned off                                              | -           | 19.33  | -       | uA |

|                                     |       | @3.0V 24Msystem clock, PCON = 0x01, IO output<br>low, other functions turned off                                             | -           | 21.00  | -       | μA |

|                                     |       | @5V, CSD parallel mode, WDT interrupt wakes up<br>after 2s, 2ms working time, IO output low, other<br>functions turned off   | -           | 36.07  | -       | μΑ |

|                                     |       | @3.3V, CSD parallel mode, WDT interrupt wakes<br>up after 2s, 2ms working time, IO output low, other<br>functions turned off | _           | 33.70  | -       | μA |

| CSD                                 |       | @3.0V, CSD parallel mode, WDT interrupt wakes<br>up after 2s, 2ms working time, IO output low, other<br>functions turned off | -           | 35.10  | -       | μA |

| parallel<br>mode                    | Idle  | @5.0V, CSD parallel mode, RTC wakes up after 2s<br>interrupt, 2ms working time, IO output low, other<br>functions turned off | -           | 765.33 | -       | μA |

|                                     |       | @3.3V, CSD parallel mode, RTC wakes up after 2s<br>interrupt, 2ms working time, IO output low, other<br>functions turned off | -           | 754.67 | -       | μΑ |

|                                     |       | @3.0V, CSD parallel mode, RTC wakes up after 2s interrupt, 2ms working time, IO output low, other functions turned off       | -           | 756.33 | -       | μΑ |

| Input low<br>voltage                | VIL   | VCC=3.0~5.5V                                                                                                                 | -           | -      | 0.3*VCC | V  |

| Input high<br>voltage               | VIH   | VCC=3.0~5.5V                                                                                                                 | 0.7*V<br>CC | -      | -       | V  |

| INT0/1/2/3<br>Input low<br>voltage  | Vintl | VCC=3.0~5.5V                                                                                                                 | -           | -      | 0.3*VCC | V  |

| INT0/1/2/3<br>Input high<br>voltage | Vinth | VCC=3.0~5.5V                                                                                                                 | 0.7*V<br>CC | -      | -       | V  |

| Output low<br>voltage               | Vol   | IOL=50mA@VCC=5V                                                                                                              | -           | -      | 0.1*VCC | V  |

| Output<br>high<br>voltage    | Vон               | IOH=15mA@VCC=5V                                                                                                                     | 0.9VC<br>C | -   | - | V  |

|------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|------------|-----|---|----|

| IO sink<br>current           | IOL               | V <sub>OL</sub> =0.1VCC, @VCC=5V                                                                                                    | -          | 50  | - | mA |

| IO source<br>current         | ЮН                | V <sub>OH</sub> =0.9VCC, @VCC=5V                                                                                                    | -          | 15  | - | mA |

| Input<br>Leakage<br>current  | I <sub>Le</sub>   | VCC=5V                                                                                                                              | -          | 1   | - | μA |

| Pull-up<br>resistor          | R <sub>P_u</sub>  | VCC=5V                                                                                                                              | -          | 10  | - | kΩ |

| Pull-down<br>resistor        | R <sub>P_d</sub>  | VCC=5V                                                                                                                              | -          | 10  | - | kΩ |

| ADC<br>Operating<br>current  | Iadc              | @5V, 24M system clock without load, IO output low,<br>enable ADC and turn on one channel, GET_ADC<br>scan, turn off other functions | -          | 1.6 | - | mA |

| LVDT<br>Operating<br>current | Ilvdt             | @5V, 24M system clock without load; in sleep<br>mode, IO output low, enable LVDT, turn off other<br>functions                       | -          | 0.6 | - | μA |

| CSD<br>Operating<br>current  | Icsd              | @5V 24M system clock without load, IO output low,<br>enable 6 channels of CSD and Timer0, turn off other<br>functions               | -          | 1.2 | - | mA |

| PWM0<br>Operating<br>current | I <sub>PWM0</sub> | @5V 24M system clock without load, IO output low,<br>enable PWM0, initate OC1 channel to 4K, turn off<br>other functions            | -          | 1.0 | - | mA |

| PWM1<br>Operating<br>current | Ipwm1             | @5V 24M system clock without load, IO output low,<br>enable PWM1, initate OC1 channel to 4K, turn off<br>other functions            | -          | 0.5 | - | mA |

| EEPROM<br>Erase<br>current   | I_E               | @5V 24M system clock without load, IO output low,<br>erase EEPROM in While, turn off other functions                                | -          | 3.3 | - | mA |

| EEPROM<br>Write<br>current   | I_w               | @5V 24M system clock without load, IO output low, write a byte in While, turn off other functions                                   | -          | 3.9 | - | mA |

## 2.3 ADC characteristics

| Table 0.7 ADC characteristics (Tamb - 25 C, diffess otherwise specified) |                                                                         |                      |      |     |      |         |  |  |

|--------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------|------|-----|------|---------|--|--|

| ADC electrical o                                                         | ADC electrical characteristics VDD=Vmin-5.5V, GND=0V, TA=+25 $^\circ$ C |                      |      |     |      |         |  |  |

| Parameter                                                                | Symbol                                                                  | Conditions           | Min  | Тур | Max  | Unit    |  |  |

| Supply voltage                                                           | Vad                                                                     | -                    | 3.0  | -   | 5.5  | V       |  |  |

| Accuracy                                                                 | N <sub>R</sub>                                                          | -                    | -    | 9   |      | Bit     |  |  |

| A/D input voltage                                                        | VAIN                                                                    | -                    | VSS  | -   | VREF | V       |  |  |

| A/D input registeres                                                     | D                                                                       | VCC=5V, RC filter    | -    | 12  | -    | kΩ      |  |  |

| A/D input resistance                                                     | RAIN                                                                    | VCC=5V, NO RC filter | -    | 2.3 | -    | kΩ      |  |  |

| A/D operating current                                                    | I <sub>AD</sub>                                                         | -                    | -    | 0.9 | -    | mA      |  |  |

| A/D input current                                                        | I <sub>ADIN</sub>                                                       | -                    | -    | -   | 1    | μA      |  |  |

| Differential Non-linearity error                                         | Dle                                                                     | VDD=5.0V             | -    | ±4  | -    | LSB     |  |  |

| Integral Non-linearity error                                             | LLE                                                                     | VDD=5.0V             | -    | ±4  | -    | LSB     |  |  |

| ADC sampling time                                                        | Tad                                                                     | -                    | 1.33 | -   | 1024 | μs      |  |  |

| ADC conversion time                                                      | TCON                                                                    | -                    | 7.75 | -   | 1079 | μs      |  |  |

| Resolution                                                               | ADCRESO                                                                 | -                    |      | 12  |      | Bit     |  |  |

| Input channel                                                            | -                                                                       | -                    | -    | -   | 25   | Channel |  |  |

Table 0.7 ADC characteristics ( $T_{amb} = 25^{\circ}C$ , unless otherwise specified)

### 2.4 Absolute Maximum Ratings

| Parameter                      | Symbol    | Min     | Тур  | Мах     | Unit |

|--------------------------------|-----------|---------|------|---------|------|

| Supply voltage                 | VCC       | VSS+3.0 | -    | VSS+5.5 | V    |

| Storage temperature            | Tstg      | -55     | -    | 150     | °C   |

| Operating temperature          | Totg      | -40     | -    | 125     | °C   |

| I/O input voltage              | Vin       | VSS-0.5 | -    | VCC+0.5 | V    |

| IOL total current              | IOLA      | -       | 100  | -       | mA   |

| IOH total current              | IOHA      | -       | -100 | -       | mA   |

| I/O ESD voltage                | ESD(HBM)  | -8      | -    | 8       | kV   |

| LATCH UP @T <sub>A</sub> =25°C | I Trigger | -200    |      | 200     | mA   |

Table 0.6Absolute maximum ratings

Note: Stresses beyond those listed absolute maximum ratings may cause permanent damage to the device. The functional operation of the device may not be predicted beyond those indicated under recommended operating conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

### 3 Memories

#### 3.1 FLASH

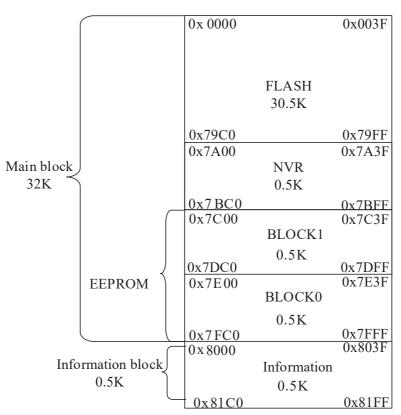

Consisted of one block of 32KB and one block of 512bytes, the flash of BS9000AMxx can erase and write 10k times, and data is not lost after the brown-out. The allocation inside the Flash is as follows:

1 page = 512Bytes

Figure 0.1 FLASH IP Memory Allocation

The flash has two blocks, which is Main block and information block, The last 1K of the main storage block is used for EEPROM functionality. The Main block can store the IC execution program. The information block is used for the storage of the configuration word information.

FLASH serves to solidify the user's programme and store the execution program.

NVR (KEY sector) is invisible to CPU and can not be written and read. This page can not be erased when the read protection is valid.

EEPROM area, can support CPU read and erase at any time, and is not protected by Flash read and write control.

The size of each page is 512 Bytes. The main block has 64 pages and the information block has 1 page.

FLASH Features is as follows:

- The Flash program uses 2-wire programming by multiplexing the PA[0](PGC) and PA[1](PGD) with the programming frequency ranging from 100K to 5M (allowing an error of 10%) and supports batch programming mode.

- Supports read protection and configuration word write protection

- BOOT program: it can be configured to disable Write protection, erase the Main block page and performs the byte write operation in the user code.

- Read out the code information stored in Flash when CPU is at working.

- Address overflow flag

#### 3.2 FLASH Read and Write Protection

#### 3.2.1 FLASH Write Protection

Write protection is configured by CFG\_WPROTECT\_PAGE. By default, the flash space protection is enabled. See Write Protection Control Range below.

| WPROTECT_PAGE | Write Protection Range |

|---------------|------------------------|

| 0             | Not protected          |

| 1             | NVR+0x0000-0x01FF      |

| 2             | NVR+0x0000-0x03FF      |

| 3             | NVR+0x0000-0x05FF      |

| 4             | NVR+0x0000-0x07FF      |

| 5             | NVR+0x0000-0x09FF      |

| 6             | NVR+0x0000-0x0BFF      |

|               |                        |

| 60            | NVR+0x0000-0x77FF      |

| 61/62/63      | NVR+0x0000-0x79FF      |

Table 0.2 Write Protection Mapping

Note:

- 1. Write protection is solely used for CPU erase and write FLASH and do not limit program mode.

- 2. EEPROM sector supports CPU erase and write operation at any time and is without SFR write protection control.

- 3. INFORMATION sector does not support CPU erase and write operation at any time and is without Write protection control.

- KEY NVR sector do not support CPU erase and write operation at any time and is without Write protection control. Note that 32 bytes from 0x7be0 to 0x7bff do not open to CPU operations and CPU can not read.

#### 3.2.2 FLASH Read Protection

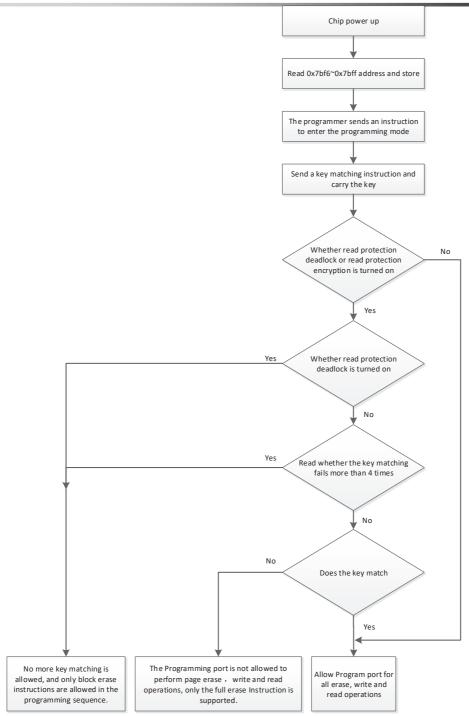

FLASH provides read protection functions including read protection deadlock and read protection encryption. The difference between them is that the latter can temporarily disable read protection by sending a decryption command in programming mode, while the former cannot. See the specific FLASH mapping below.

| Flash address (0x7bf6~0x7bf9)<br>4byte is used to store the number of key<br>attempts                     | Flash address (0x7bfa~0x7bfd)<br>4byte is used to store the key                  | Flash address (0x7bfe)<br>1byte is used to store whether<br>read protection encryption is<br>enabled (0x83) | Flash address (0x7bff)<br>lbyte is used to store whether to<br>enable read protection deadlock<br>(0x68) |

|-----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|

| When mass production and<br>programming, it is necessary to ensure<br>that the address range data is 0xFF | During mass production, the key, read pu<br>along with the HEX file, and the key | 1                                                                                                           | 1 0 1                                                                                                    |

Figure 3.3 Read Protection

See below the Read Protection Control Flow Chart in programming mode.

Figure 0.4 Read Protection Control Flow Chart in Programming Mode

Note

- When the Read Protection is valid, the debug port is invalid and can not work upon any commands.

- When the Read Protection is invalid, all space can be read by CPU, SWE,PG except the address from 0x7BE0 to 0x7BFF which can not be read by CPU.

#### BS9000AMxx

- When the Read Protection is valid, CPU cannot read the address from 0x7BE0 to 0x7BFF. SWE can not be read in any way except after keys match in programming mode (Read protection lock dose not support KEY Match to unlock).

- No limit on EEPROM (0x7c00 to 0x7fff) and INFORMATION (0x8000 to 0x81ff) to be read at any time.

- If the Read Protection Lock is enabled, it is not allowed to match keys in code mode and support no operations except the command Erase all.

- If only the Read protection encryption is enabled, the code mode allows erase page, write page and read page when keys match, otherwise just Erase all is allowed.

- If only the Read protection encryption is enabled, code mode allows keys match operation. If the number of mismatches is greater than 4, the matching operation is no longer allowed, and only the full erase instruction is allowed to execute.

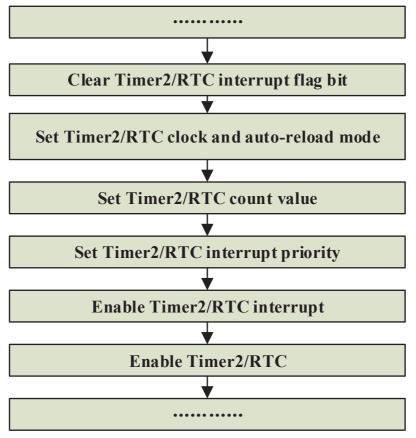

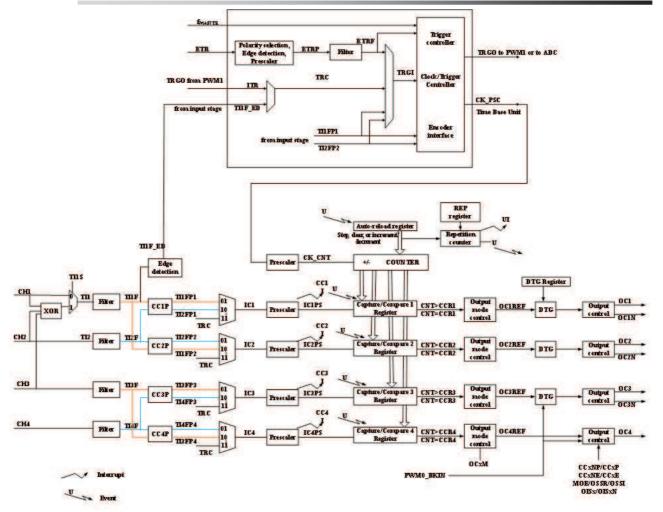

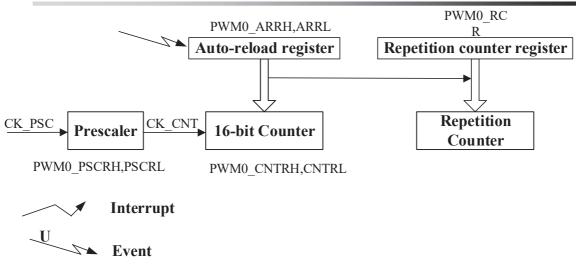

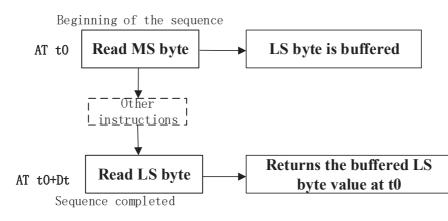

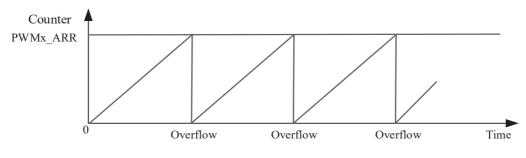

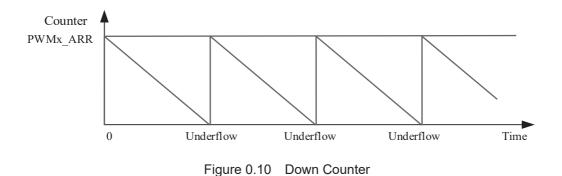

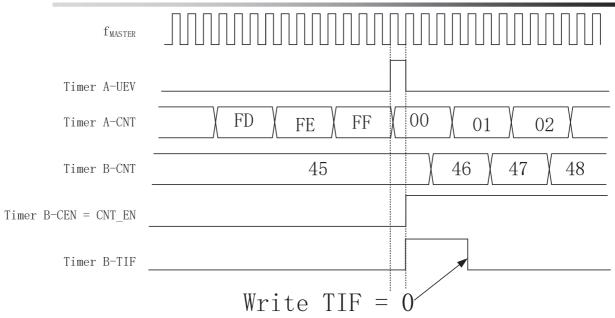

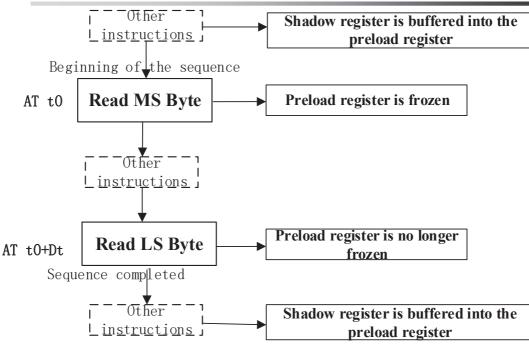

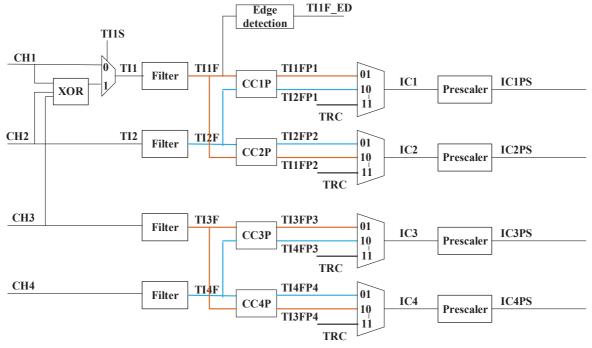

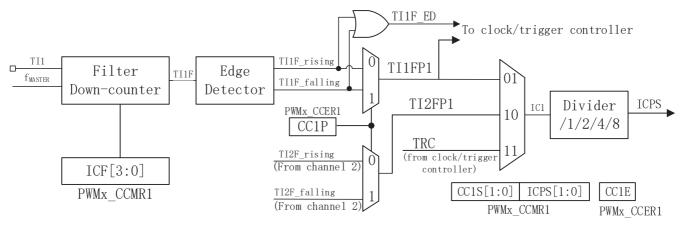

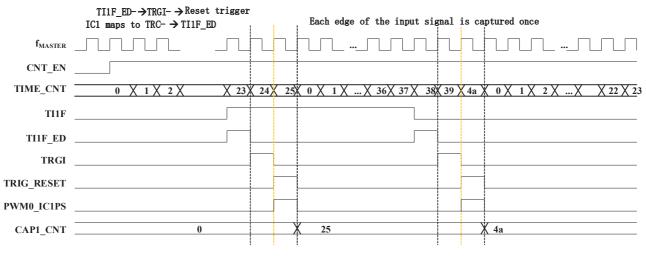

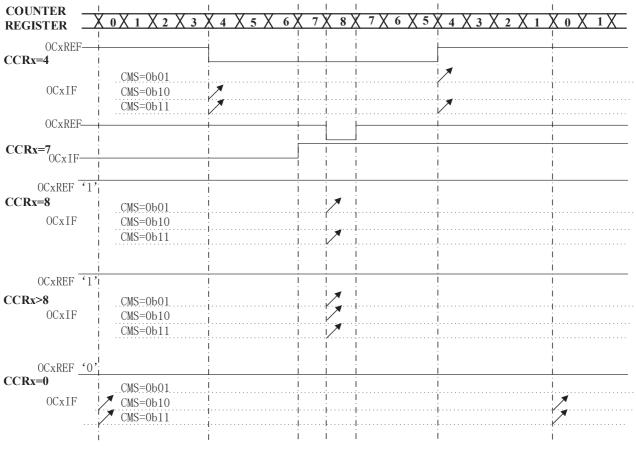

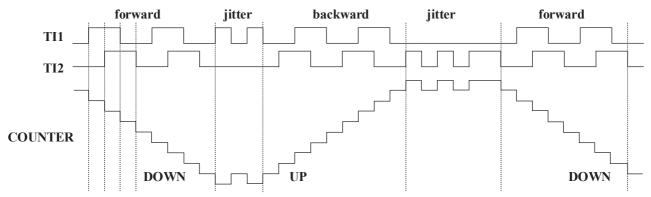

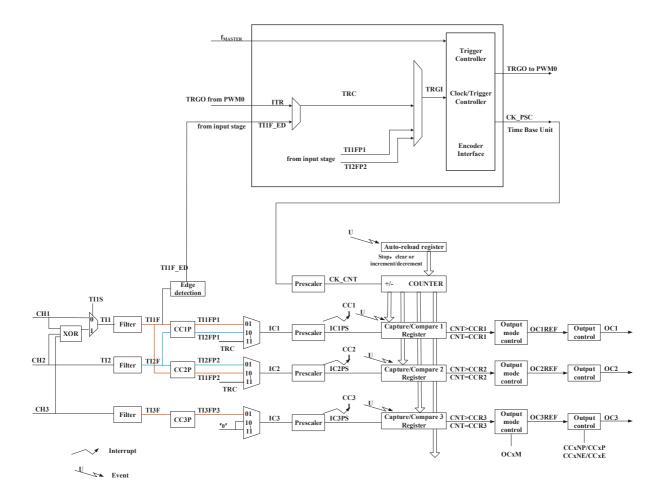

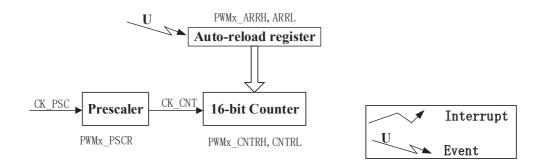

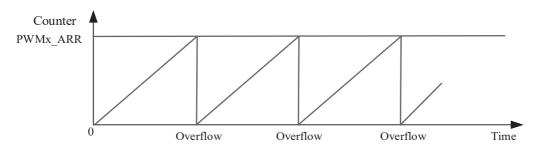

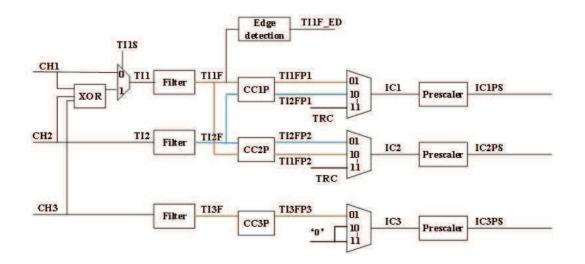

- The configuration bit of Read protection lock is 0x68. The configuration bit of read protection encryption is 0x83.